- ��IC�ؼ���

�����������ŵ��ӿƼ�����˾

- ���һ��֣�

Ӫҵִ�գ��������Ӫģʽ��ó��/����/�������ڵ������㶫 ������ҵ��վ��

Ӫҵִ�գ��������Ӫģʽ��ó��/����/�������ڵ������㶫 ������ҵ��վ��

http://www.zlxele.com

�ղر���˾ ������665060

��ҵ����

- ���֤����

- ��Ա���ͣ�

- ��Ա���ޣ�13��

- ����IM��

- ��ַ�������и���������·�ʺ��¶����ò�����7A��

- ���棺0755-23956688

- E-mail��sales@zlxele.com

��Ʒ����

���ɵ�·(IC)(1273)

�뵼��洢��(1)

������(2)

��Ƭ��(1)

������(1)

��Դ/��ѹ��(3)

ʯӢ��������(1)

������/�Ӳ��(1)

����(1)

������(23)

�Ŵ���(15)

�������(2)

LMK04208NKDT Texas Instruments ʱ�Ӻϳ���/��������� Ultra Low Noise Clock Jitter Cleaner With 6

7 Output

LVCMOS, LVDS, LVPECL

3072 MHz

WQFN-64

��ز�Ʒ

��Ʒ��Ϣ

1 Features

1• Ultra-Low RMS Jitter Performance

�C 111 fs, RMS Jitter (12 kHz to 20 MHz)

�C 123 fs, RMS Jitter (100 Hz to 20 MHz)

• Dual Loop PLLatinum™ PLL Architecture

• PLL1

�C Integrated Low-Noise Crystal Oscillator Circuit

�C Holdover Mode when Input Clocks are Lost

�C Automatic or Manual Triggering/Recovery

• PLL2

�C Normalized PLL Noise Floor of �C227 dBc/Hz

�C Phase Detector Rate of Up to 155 MHz

�C OSCin Frequency-Doubler

�C Integrated Low-Noise VCO or External VCO

Mode

2 Applications

• Data Converter Clocking

• Wireless Infrastructure

• Networking, SONET/SDH, DSLAM

• Medical, Video, Military, Aerospace

• Test and Measurement

3 Description

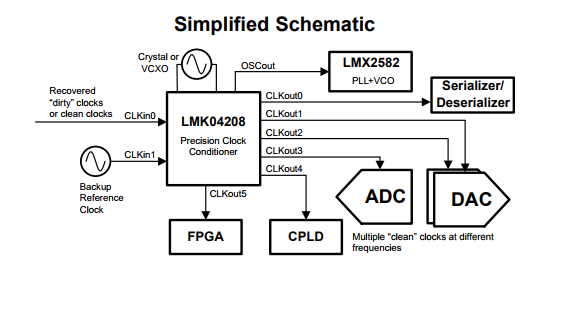

The LMK04208 is a high performance clock

conditioner with superior clock jitter cleaning,

generation, and distribution with advanced features to

meet next generation system requirements. The dual

loop PLLatinum™ architecture is capable of 111 fs,

RMS jitter (12 kHz to 20 MHz) using a low-noise

VCXO module or sub-200 fs rms jitter (12 kHz to 20

MHz) using a low cost external crystal and varactor

diode.

The dual loop architecture consists of two highperformance

phase-locked loops (PLL), a low-noise

crystal oscillator circuit, and a high-performance

voltage controlled oscillator (VCO). The first PLL

(PLL1) provides low-noise jitter cleaner functionality

while the second PLL (PLL2) performs the clock

generation. PLL1 can be configured to either work

with an external VCXO module or the integrated

crystal oscillator with an external tunable crystal and

varactor diode. When paired with a very narrow loop

bandwidth, PLL1 uses the superior close-in phase

noise (offsets below 50 kHz) of the VCXO module or

the tunable crystal to clean the input clock. The

output of PLL1 is used as the clean input reference to

PLL2 where it locks the integrated VCO. The loop

bandwidth of PLL2 can be optimized to clean the farout

phase noise (offsets above 50 kHz) where the

integrated VCO outperforms the VCXO module or

tunable crystal used in PLL1.